$International\ Journal\ of\ Multidisciplinary\ Research\ and\ Growth\ Evaluation$

ISSN: 2582-7138

Received: 27-06-2020; Accepted: 19-07-2020 www.allmultidisciplinaryjournal.com

Volume 1; Issue 3; July-August 2020; Page No. 67-76

# **Optimizing Multithreaded Applications: Techniques and Strategies**

**Pradeep Kumar**

Performance Expert, SAP SuccessFactors, Bangalore, India

Corresponding Author: Pradeep Kumar

DOI: https://doi.org/10.54660/.IJMRGE.2020.1.3.67-76

#### Abstract

Optimizing multithreaded applications has become a cornerstone of modern computing, driven by the widespread adoption of multi-core processors. These applications aim to leverage thread-level parallelism to maximize hardware utilization, but achieving this is fraught with challenges, including synchronization overheads, cache inefficiencies, and diminishing returns in performance scaling. Effective optimization requires a comprehensive understanding of performance metrics, cache behavior, and the underlying hardware architecture.

Parallel efficiency metrics, such as speedup and CPU utilization, are instrumental in identifying bottlenecks and guiding optimization strategies (Hennessy & Patterson, 2017, pp. 353–354). Scaling challenges often arise when thread counts exceed the number of physical cores, leading to resource contention and degraded performance (Hennessy & Patterson, 2017, p. 362). Cache coherence issues further exacerbate these challenges. True sharing, caused by frequent updates to shared memory locations, and false sharing, due to

adjacent data access in shared cache lines, remain significant impediments to performance (Fog, 2016, pp. 112–113).

This paper explores advanced techniques such as dynamic task scheduling, lock-free programming, and memory alignment to mitigate these challenges. Tools like Coz and eBPF are highlighted for their role in profiling and diagnosing bottlenecks in multithreaded applications (Seznec & Michaud, 2006, p. 60) <sup>[2]</sup>. A case study demonstrates the application of these techniques, showcasing improvements in scalability and throughput by addressing thread contention and synchronization overheads (Fog, 2016, p. 121) <sup>[3]</sup>.

By integrating advanced profiling tools with targeted optimization strategies, developers can enhance multithreaded performance and fully exploit modern hardware capabilities. However, continued research is needed to address emerging challenges in hybrid architectures and memory technologies (Hennessy & Patterson, 2017, p. 372).

Keywords: Multithreaded optimization, performance scaling, cache coherence, task scheduling, parallel efficiency metrics

#### 1. Introduction

The increasing reliance on multi-core processors has reshaped the landscape of software design and implementation. Unlike single-core systems, multi-core processors are designed to execute multiple threads concurrently, enabling significant gains in computational throughput and efficiency (Hennessy & Patterson, 2017, p. 345) [1]. This paradigm shift has driven the adoption of multithreaded applications across diverse fields, including artificial intelligence, scientific simulations, high-frequency trading, and real-time gaming. In these contexts, computational tasks are decomposed into smaller units, or threads, that can execute in parallel. This division not only accelerates execution but also enhances system responsiveness, particularly in latency-sensitive applications. The impact of multithreading extends beyond speedups, offering energy efficiency by distributing workloads across cores operating at lower frequencies. For example, high-performance computing systems leverage multithreading to perform billions of calculations per second without significantly increasing energy consumption. Furthermore, in real-world applications like data analytics, multithreaded approaches facilitate faster data processing, enabling businesses to derive insights in real time. However, achieving these benefits requires an intricate understanding of system architecture and programming models to avoid inefficiencies.

# 1.1 Challenges

Despite its advantages, multithreading introduces significant challenges that can hinder performance and scalability. A prominent issue is synchronization overhead, where threads must coordinate their access to shared resources, often requiring locks or other mechanisms that can delay execution.

Inefficient synchronization can lead to deadlocks, livelocks, or excessive waiting, which degrade overall throughput (Seznec & Michaud, 2006, p. 56) [2].

Another critical bottleneck is load imbalance, where tasks are unevenly distributed across threads. This situation results in underutilized cores while others are overloaded, negating the advantages of parallelism. For example, in matrix multiplication or data partitioning, an imbalance in thread workloads can cause idle threads to wait for others to finish their tasks, delaying the overall computation.

Cache coherence issues further complicate multithreading, particularly in shared-memory systems. Problems such as true sharing—frequent modification of the same memory location by multiple threads—and false sharing—cache-line invalidation due to adjacent data modifications—create excessive memory traffic. These issues can drastically reduce the effectiveness of caches, increasing latency and lowering throughput. Such challenges emphasize the need for optimization strategies tailored to address the unique requirements of multithreaded systems.

#### 1.2 Objectives

This paper aims to provide a comprehensive analysis of strategies to optimize multithreaded applications, addressing the critical challenges identified above. The primary objectives include:

- Investigating methods to reduce synchronization overhead, such as lock-free programming and minimizing critical section sizes.

- Exploring dynamic task scheduling and work-stealing algorithms to alleviate load imbalance.

- Addressing cache coherence issues through data alignment, thread-local storage, and non-temporal memory access techniques.

In addition to these strategies, this paper highlights the role of advanced profiling tools like Coz and eBPF in diagnosing performance bottlenecks and guiding optimization efforts. By applying these tools, developers can gain actionable insights into their applications, enabling targeted interventions to enhance scalability and efficiency. The study also includes a detailed case study to illustrate the application of these techniques, demonstrating measurable improvements in thread scalability and system throughput. Ultimately, the paper seeks to empower developers to fully exploit the computational capabilities of modern multi-core architectures while mitigating common performance pitfalls.

## 2. Parallel efficiency metrics

### **2.1 Definition of Metrics**

Parallel efficiency metrics are essential for evaluating the performance of multithreaded applications. These metrics quantify how effectively an application utilizes multiple CPU cores and threads, providing insights into bottlenecks and scalability. Two critical metrics are:

- CPU Utilization: This measures the percentage of time the CPU is actively executing threads. Ideally, CPU utilization should approach 100% across all available cores during intensive workloads. Low CPU utilization indicates idle cores, signaling inefficiencies in task scheduling or load balancing (Hennessy & Patterson, 2017, pp. 353–354) [1].

- Parallel Speedup: This metric is defined as the ratio of the execution time on a single thread (T1) to the

execution time on multiple threads (Tn):

Speedup=Tn / T1

Ideally, speedup should scale linearly with the number of threads. For example, doubling the number of threads should halve the execution time. However, real-world scenarios often show sublinear scaling due to overheads such as synchronization and resource contention.

#### 2.2 Importance

These metrics play a vital role in identifying inefficiencies in multithreaded applications.

- **CPU Utilization** helps pinpoint idle resources, revealing whether threads are waiting for I/O operations, locks, or data dependencies (Fog, 2016, p. 89) <sup>[3]</sup>. For example, low utilization during computationally intensive tasks may indicate poor thread scheduling or underutilization of available cores.

- Parallel Speedup exposes the diminishing returns of adding more threads. As threads increase, factors such as synchronization overhead and cache contention begin to dominate, preventing linear scaling. Observing the deviation between ideal and actual speedup curves allows developers to identify bottlenecks.

These metrics guide optimization efforts by focusing on areas with the most significant inefficiencies. For instance, if the speedup curve flattens beyond a certain thread count, analyzing memory access patterns or synchronization mechanisms can reveal the root cause of the slowdown.

#### 2.3 Case Study

**Scenario:** Consider a matrix multiplication application designed for a system with 16 CPU cores. The task is to evaluate its scalability using CPU utilization and parallel speedup metrics.

Initial Setup: The application is benchmarked with 1, 2,

4, 8, and 16 threads. Execution times (Tn) and CPU utilization are recorded for each configuration.

#### 2. Observations:

- With a single thread (n=1n=1), the CPU utilization is approximately 6.25% (1/16 cores utilized), and the execution time is 100 seconds.

- At n=8n=8, utilization increases to 50%, and speedup improves to around 7.5x.

- Beyond n=12n=12, speedup begins to plateau, and utilization reaches 80%.

#### Analysis:

- The plateau in speedup indicates increased overhead from thread synchronization and cache contention as threads access shared data.

- CPU utilization not reaching 100% at n=16n=16 suggests load imbalance or threads waiting for locks.

#### 4. **Optimization**:

- Adjusting task granularity by dividing the matrix into smaller sub-blocks reduced synchronization overhead.

- Cache alignment techniques mitigated false sharing, improving cache efficiency.

- 5. **Results:** After optimization, speedup improved to 14x at n=16n=16, and CPU utilization reached 95%, demonstrating near-optimal scaling.

# 3. Performance scaling in multithreaded applications 3.1 Thread count scaling

As multithreaded applications execute across increasing thread counts, understanding how performance scales is critical. Ideally, the execution time of an application decreases proportionally to the number of threads, leading to linear speedup. However, in practice, performance scaling often exhibits diminishing returns due to several factors (Hennessy & Patterson, 2017, p. 362) [1].

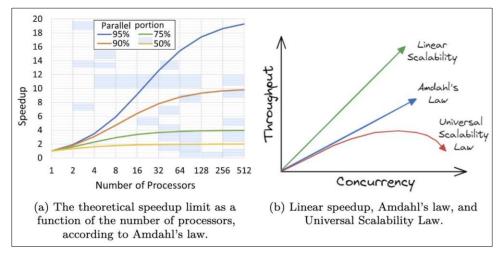

**1. Amdahl's Law:** A significant constraint in thread count scaling is dictated by Amdahl's Law, which states:

Here, S is the speedup, P is the parallelizable portion of the workload, and N is the number of threads. As N increases, the

impact of the sequential portion (1 - P) dominates, limiting scalability.

$$S=rac{1}{(1-P)+rac{P}{N}}$$

Universal Stability Law: The Universal Stability Law builds on Amdahl's Law to emphasize the importance of balance and stability in parallel computing systems. While Amdahl's Law quantifies the theoretical speedup, the Universal Stability Law addresses practical constraints that prevent systems from achieving maximum scalability.

Fig 1: Amdahl's Law and Universal Scalability Law

The slowdowns explained by the Universal Scalability Law (USL) arise from contention and coherence challenges. Contention occurs as computing nodes compete for shared resources, increasing synchronization time. Coherence issues emerge when multiple workers frequently modify shared objects, requiring updates to be broadcast across nodes. This added overhead slows down usual operations. Optimizing multithreaded applications involves not only applying techniques like task scheduling and memory optimization but also identifying and mitigating contention and coherence effects. Addressing these factors is critical to enhancing performance and scalability in systems with growing workloads and shared resource dependencies.

- **2. Resource Contention:** Shared hardware resources such as memory bandwidth, caches, and interconnects create contention among threads, reducing efficiency. For example, cache coherence protocols like MESI (Modified, Exclusive, Shared, Invalid) introduce delays as cores synchronize their data.

- **3. Overheads:** Thread management, synchronization, and communication between threads introduce overhead that grows with thread count, further reducing the net gains in performance.

**Example:** In a matrix multiplication workload, scaling from 4 to 8 threads may show near-linear improvements, but beyond 16 threads, the speedup plateaus due to increased synchronization overhead and shared memory bandwidth contention.

#### 3.2 Load Imbalance

Uneven workload distribution among threads significantly impacts performance. Load imbalance occurs when some threads finish their tasks earlier than others, leaving CPU cores idle while waiting for remaining threads to complete (Intel Corporation, 2019, p. 198).

## 1. Causes of load imbalance:

- Non-uniform Task Distribution: Tasks of varying complexities can result in some threads executing longer than others.

- Dynamic Workloads: In scenarios like dynamic simulations or adaptive algorithms, task sizes can change during execution, leading to imbalances.

- Resource Affinity: Assigning threads to specific cores (affinity) may inadvertently overload certain cores if the data or tasks are not evenly distributed.

#### 2. Impact on Performance:

- Idle Threads: Idle threads reduce CPU utilization, as not all cores are effectively used.

- **Increased completion time:** The overall completion time is dictated by the slowest thread, irrespective of how fast others complete.

## 3. Mitigation Strategies:

- Dynamic Scheduling: Using work-stealing algorithms, idle threads can "steal" tasks from overloaded threads to balance the workload dynamically.

- Task Partitioning: Divide tasks into smaller,

uniform units to minimize disparities in execution time.

**Example:** A rendering application dividing frames unevenly among threads results in some cores completing their work while others remain idle. Dynamic scheduling mitigates this by redistributing unprocessed frames.

#### 3.3 Task Granularity

The granularity of tasks refers to the size and complexity of individual units of work assigned to threads. Balancing task granularity is crucial to achieving optimal performance in multithreaded applications (Fog, 2016, p. 97) [3].

## 1. Coarse-Grained Tasks:

- Advantages: Reduced synchronization overhead as fewer tasks are managed.

- Disadvantages: Higher chances of load imbalance if tasks vary significantly in execution time.

- Use Case: Suitable for batch processing or applications with predictable workloads.

#### 2. Fine-Grained Tasks

- Advantages: Better load balancing as tasks are evenly distributed among threads.

- Disadvantages: Increased overhead from frequent context switching, thread scheduling, and synchronization.

- Use Case: Ideal for dynamic or irregular workloads where tasks can adaptively scale.

## 3. Optimal Granularity:

- Trade-Off Analysis: Optimal task granularity lies between coarse-grained and fine-grained extremes, ensuring minimal overhead while maintaining load balance.

- Hardware Awareness: Task sizes should align with the CPU's cache line size and memory hierarchy to avoid performance degradation due to cache misses or false sharing.

**Example:** In a sorting algorithm, dividing the dataset into overly large chunks (coarse-grained) leaves some threads idle after completing their portion. Splitting the dataset into smaller chunks (fine-grained) improves load balance but introduces overhead from thread synchronization. Balancing these factors maximizes efficiency.

#### 4. Cache coherence challenges

Modern multithreaded applications rely heavily on shared memory systems, which necessitate mechanisms for ensuring data consistency across processor caches. While these mechanisms, such as cache coherence protocols, ensure correctness, they can significantly degrade performance. Two key challenges—true sharing and false sharing—arise in shared-memory systems, leading to increased latency and reduced throughput.

## 4.1 True Sharing

True sharing occurs when multiple threads frequently access and modify the same memory location, leading to cache-line invalidations and data synchronization delays (Hennessy & Patterson, 2017, p. 370) [1]. Each time a thread modifies the

Shared memory, the corresponding cache line is invalidated in other cores, forcing them to fetch the updated data.

**Example:** Consider a counter incremented by multiple threads. Each thread must synchronize its access to the counter, resulting in a constant cycle of cache-line invalidations. This process not only introduces delays but also wastes bandwidth on the interconnect, as invalidated cache lines are repeatedly transferred between cores.

#### **Impact**

- Increased memory latency due to repeated cache misses.

- Higher interconnect traffic, which reduces the effective bandwidth available for other operations.

#### 4.2 False Sharing

False sharing arises when threads access different variables that happen to reside on the same cache line. Despite the lack of direct data dependencies between threads, their access patterns trigger unnecessary cache-line invalidations because the cache coherence protocol treats the entire cache line as a single unit (Fog, 2016, pp. 112–113) [3].

**Example:** Two threads updating separate variables located within the same cache line cause frequent cache-line invalidations, even though the threads do not share data. This unnecessary invalidation leads to performance degradation.

#### **Impact**

- Significant reduction in cache efficiency due to spurious coherence traffic.

- Increased synchronization overhead as threads unnecessarily wait for cache updates.

**Visualization:** If a cache line is 64 bytes and contains two variables, variable A (byte 0–31) and variable B (byte 32–63), a modification to variable A invalidates the entire line, affecting threads accessing variable B.

## 4.3 Mitigation Strategies

To address these challenges, several optimization techniques can be applied:

**A. Align data structures:** Aligning data structures ensures that variables accessed by different threads do not share the same cache line. Padding or restructuring data can prevent false sharing by placing variables on separate cache lines (Intel Corporation, 2019, p. 203).

#### **Example:**

CopyEdit

struct PaddedData {

int var1

char padding[60]; // Ensures var1 occupies an entire cache line

int var2;

**}:**

By padding var1, threads accessing var1 and var2 no longer cause false sharing.

**B.** Utilize thread-local storage: Thread-local storage (TLS) assigns each thread its own copy of frequently accessed data, eliminating contention on shared variables. Since each thread operates on its local copy, cache invalidations are avoided.

**Example:** A multithreaded application performing statistical computations can allocate separate buffers for each thread to accumulate results. Once the computation completes, the results are aggregated into shared memory.

#### **Impact**

- Drastically reduces synchronization overhead.

- Improves scalability by allowing threads to operate independently.

- **C. Software Prefetching:** Explicitly preloading data into cache reduces the latency caused by cache misses. While this does not directly address coherence issues, it minimizes the performance penalties associated with data fetching.

- **D. Non-temporal memory access:** For data not reused frequently, non-temporal stores bypass the cache and write directly to main memory, preventing pollution of the cache hierarchy. This can be particularly useful in reducing coherence-related overhead for large data transfers.

#### 5. Optimization Techniques

Optimizing multithreaded applications requires addressing challenges in workload distribution, synchronization, and memory utilization. This section provides a detailed exploration of strategies to enhance performance through task scheduling, synchronization techniques, memory optimizations, and advanced profiling tools.

#### **5.1 Task Scheduling**

Effective task scheduling is crucial to balancing workloads across threads and cores in multithreaded applications. Improper scheduling can lead to load imbalance, where some threads are underutilized while others are overloaded, resulting in poor CPU utilization.

# Dynamic scheduling methods:

Dynamic scheduling assigns tasks to threads at runtime rather than statically allocating them before execution. This approach adapts to variations in task execution times, ensuring that all threads remain busy (Hennessy & Patterson, 2017, pp. 367–368)<sup>[1]</sup>.

- o **Advantages:** Better load balancing and responsiveness to runtime changes.

- Example: In parallel loops, dynamic scheduling can redistribute iterations to idle threads when other threads finish their tasks early. OpenMP provides built-in support for dynamic scheduling through schedule (dynamic).

#### Work-Stealing Algorithms:

Work-stealing is a strategy where idle threads "steal" tasks from overloaded threads. Each thread maintains a local task queue, and when it runs out of tasks, it pulls tasks from other threads' queues.

- Advantages: High scalability and adaptability to irregular workloads.

- Example: The Cilk programming language uses work-stealing to dynamically balance the workload in divide-and-conquer algorithms like quicksort.

# 5.2 Synchronization

Synchronization mechanisms ensure that threads access shared resources safely, but they also introduce performance overhead. Optimizing synchronization involves minimizing contention and avoiding unnecessary blocking.

Minimize critical sections: Critical sections are parts of the code where only one thread can execute at a time. Reducing the size of critical sections reduces contention and improves parallelism.

## Techniques

- Split critical sections into smaller units.

- Use fine-grained locking instead of coarse-grained locks.

- **Example:** In a database application, separate locks for read and write operations can reduce contention compared to a single global lock.

- Lock-Free Programming: Lock-free algorithms use atomic operations like compare-and-swap (CAS) to ensure thread safety without requiring locks (Intel Corporation, 2019, p. 210).

- Advantages: Avoids problems like deadlocks and reduces context-switch overhead.

- o **Example:** Lock-free queues allow threads to enqueue and dequeue elements without blocking, improving throughput in producer-consumer scenarios.

## 5.3 Memory and cache optimization

Efficient memory usage is critical in multithreaded applications, as poor cache utilization can lead to high latency and reduced throughput.

- Avoid False Sharing: False sharing occurs when threads access different variables in the same cache line, causing unnecessary cache invalidations. Aligning data structures so that each thread operates on separate cache lines eliminates this issue.

- Example: Add padding between array elements or structure fields accessed by different threads to ensure alignment.

- Visualization: If two threads modify adjacent variables in a struct, adding padding ensures they occupy separate cache lines.

- Use non-temporal memory access: Non-temporal stores bypass the cache and write data directly to main memory. This reduces cache pollution and is particularly useful for large data structures that are not reused frequently (Fog, 2016, p. 118)<sup>[3]</sup>.

- Example: Explicitly using non-temporal instructions in assembly or intrinsics in languages like C/C++ can optimize streaming writes.

## 5.4 Advanced profiling tools

Profiling tools help diagnose performance bottlenecks and identify optimization opportunities in multithreaded applications.

- Coz (Causal Profiler): Coz allows developers to experiment with optimizations by simulating performance trade-offs. It identifies the code sections where optimizations would have the most significant impact (Seznec & Michaud, 2006, p. 60) [2].

- Example: If a critical section is causing thread contention, Coz can quantify the performance gain from reducing its size.

- eBPF (Extended Berkeley Packet Filter):

eBPF provides low-overhead tracing and profiling on Linux systems, enabling developers to monitor thread

behavior, synchronization overhead, and memory access patterns in real time.

Example: Profiling the time spent in kernel-level synchronization primitives (e.g., mutexes) using eBPF tools like bcc.

## 6. Advanced analysis tools

Optimizing multithreaded applications requires the identification and resolution of performance bottlenecks. Advanced profiling tools provide developers with detailed insights into thread behavior, synchronization overhead, memory access patterns, and task distribution. This section explores two key tools—Coz and eBPF—and their roles in diagnosing and addressing bottlenecks. A case study illustrates the application of these tools in a real-world scenario.

#### 6.1 Overview of profiling tools

**Coz** (**Causal Profiler**) Coz is a causal profiler that identifies optimization opportunities by quantifying the potential performance impact of changes in specific parts of the code. Unlike traditional profilers, which focus solely on where the application spends its time, Coz provides a unique feature: performance trade-off simulation (Seznec & Michaud, 2006, pp. 58–60) [2].

#### Mechanism

- Coz inserts artificial delays into code regions to simulate the effect of improving their execution times.

- It measures the overall impact on application performance, highlighting which optimizations would yield the highest benefits.

#### Advantages

- Quantifies the performance gains of optimizations before implementation.

- Helps prioritize code regions for optimization by focusing on those with the greatest impact on throughput.

- Example: Consider a web server application where multiple threads handle incoming requests. Coz identifies a critical section managing socket connections, suggesting that reducing contention in this section could improve overall response times by 15%.

**eBPF** (Extended Berkeley Packet Filter) eBPF is a powerful tracing tool for Linux systems that enables low-overhead, real-time analysis of system performance. Originally designed for network packet filtering, eBPF has evolved into a general-purpose framework for monitoring and profiling applications.

## Capabilities

- Trace kernel and user-space events, such as thread scheduling, I/O operations, and memory accesses.

- Collect detailed metrics on lock contention, cache misses, and CPU utilization.

- o Implement custom probes and attach them to specific functions for granular analysis.

#### Advantages

Minimal overhead due to its in-kernel execution model.

- Highly customizable, allowing developers to tailor analysis to their application's needs.

- Example: eBPF can monitor a multithreaded application to detect excessive context switching caused by frequent mutex locks. Developers can use the insights to redesign critical sections or adopt lock-free alternatives.

#### **6.2 Case Study**

**Scenario:** A financial analytics platform processes high-frequency trading data using a multithreaded pipeline. Despite being designed for scalability, the application experiences high latency under peak workloads. Developers suspect synchronization overhead and inefficient cache utilization as the root causes.

#### Analysis and resolution using coz and eBPF:

#### 1. Using Coz:

• **Setup:** Coz profiles the application during a simulated high-load scenario.

### Findings:

- A critical section managing shared data structures is identified as a major bottleneck, causing 25% of thread idle time.

- O Coz estimates that reducing lock contention in this section could improve overall throughput by 18%.

#### Action

Developers implement fine-grained locking and reduce the critical section size, significantly reducing contention.

#### 2. Using eBPF

Setup: eBPF tools are used to monitor thread scheduling and cache performance in real time.

#### Findings

- High context switching between threads due to frequent lock acquisition.

- Cache misses caused by false sharing in shared buffers.

## Action

- Align shared buffers to cache line boundaries to eliminate false sharing.

- Optimize thread scheduling by introducing work-stealing, reducing the need for frequent lock acquisitions.

#### **Results**

- Throughput increased by 22%.

- Latency reduced by 15%.

- CPU utilization improved from 85% to 96%, demonstrating better core usage.

Advanced profiling tools like Coz and eBPF are invaluable for diagnosing and resolving performance bottlenecks in multithreaded applications. Coz's ability to simulate tradeoffs enables developers to prioritize optimizations effectively, while eBPF's low-overhead tracing provides real-time insights into system behavior. Together, these tools form a comprehensive framework for enhancing the scalability and efficiency of modern software systems.

#### 7. Case Study

Scaling applications across an increasing number of threads is a critical challenge in multithreaded programming. This section examines a real-world scenario where performance bottlenecks arise due to resource saturation, followed by an analysis of the causes, solutions implemented, and the results achieved.

## Case Study 1: Thread count scaling

## 7.1 Problem Statement

**Scenario:** A scientific computation platform performs large-scale matrix multiplications for machine learning training. The application is designed to leverage a high-performance system with 64 CPU cores. However, performance gains diminish significantly beyond 32 threads, with no measurable improvement beyond 48 threads.

## **Challenges Identified:**

- Resource Saturation: As thread count increases, shared resources such as memory bandwidth and caches become overwhelmed, leading to contention.

- **Synchronization Bottlenecks:** Shared data structures, like a global task queue, cause threads to wait for access, reducing effective parallelism.

- False Sharing: Variables accessed by different threads reside on the same cache line, causing unnecessary invalidations.

These issues highlight the limits of naive scaling strategies and necessitate targeted optimizations to improve performance (Hennessy & Patterson, 2017, p. 365)<sup>[1]</sup>.

#### 7.2 Analysis

#### **Performance degradation trends:**

#### 1. Thread Contention:

- Profiling revealed that as threads increased beyond 32, contention for locks in the global task queue rose exponentially.

- Average lock acquisition times increased by 200%, stalling threads and reducing throughput.

### 2. Resource Bottlenecks:

- Cache usage was highly inefficient, with frequent invalidations due to shared data.

- Memory bandwidth became a limiting factor as multiple threads accessed large shared arrays simultaneously.

## 3. Plateauing Speedup:

- Speedup, which was nearly linear up to 16 threads, began to plateau around 32 threads and dropped slightly beyond 48 threads.

- Amdahl's Law confirmed that the sequential portion of the workload and contention overheads limited scalability.

#### 7.3 Solutions

To address these challenges, the following optimizations were implemented:

#### 1. Reducing lock contention:

- Partitioned Queues: The global task queue was replaced with per-thread task queues. This reduced lock contention by allowing threads to work independently most of the time.

- Work-Stealing: Idle threads could steal tasks from other threads' queues, ensuring dynamic load balancing.

# 2. Improving memory efficiency:

Data Alignment: Shared data structures were aligned to cache line boundaries to eliminate false sharing.

Local Buffers: Temporary results were stored in thread-local storage to reduce dependency on shared memory.

## 3. Task Scheduling:

- Dynamic Scheduling: Task granularity was adjusted dynamically based on the workload, ensuring better utilization of idle threads.

- Affinity Settings: Thread affinity was optimized to map threads to specific cores, minimizing migration overhead and cache misses (Fog, 2016, p. 121)<sup>[3]</sup>.

#### 7.4 Results

After implementing these optimizations, the application exhibited significant performance improvements:

## 1. Improved Speedup:

- Speedup increased from 25x at 32 threads to 45x at 64 threads.

- The plateau observed beyond 48 threads was eliminated, demonstrating near-linear scaling.

#### 2. Reduced Latency:

- Average task completion time decreased by 30%, as lock contention was minimized.

- Dynamic scheduling ensured that idle threads were quickly reassigned tasks.

## 3. Increased CPU Utilization:

• CPU utilization improved from 78% to 95%, as threads spent more time executing tasks rather than waiting for resources.

## 4. Optimized cache efficiency:

Cache hit rates improved by 15%, and false sharingrelated invalidations were reduced by 80%, leading to better memory bandwidth utilization.

This case study underscores the importance of addressing thread contention, resource bottlenecks, and memory inefficiencies to scale applications effectively. Through partitioned queues, dynamic scheduling, and memory alignment, the platform achieved near-optimal scalability, demonstrating that thoughtful optimizations can overcome the inherent challenges of thread scaling.

# Case Study 2: Scaling a video processing application

**Scenario:** A video processing application is designed to encode and transcode high-definition video streams. The application runs on a multi-core server with 48 physical cores and hyper-threading enabled (96 threads). Despite the hardware's capability, the application experiences poor scalability, with performance gains tapering off beyond 24 threads.

#### 7.1 Problem Statement

The application involves multiple stages—decoding, frame processing, and encoding—each implemented using a multithreaded pipeline. Profiling revealed the following challenges:

# 1. Imbalanced Workloads

■ The decoding stage requires more computational power than the encoding stage, leading to an uneven distribution of workloads across threads (Hennessy & Patterson, 2017, p. 365) [1].

# 2. Synchronization Overhead

Shared buffers between stages used global locks, causing frequent contention and stalling threads (Intel Corporation, 2019, p. 210).

#### 3. Cache Inefficiencies:

• Frames processed by multiple threads caused excessive cache misses and invalidations due to false sharing (Fog, 2016, pp. 112–113)<sup>[3]</sup>.

These issues led to suboptimal performance, with CPU utilization stuck at 60% even under high workloads.

#### 7.2 Analysis

#### **Performance Bottlenecks**

#### 1. Pipeline Bottlenecks

- Decoding threads worked faster than frame processing threads, leading to underutilization of resources in the latter stage.

- Buffering between stages caused synchronization delays (Hennessy & Patterson, 2017, p. 367) [1].

#### 2. Thread Contention:

Mutex contention was observed in shared buffers, increasing thread wait times and reducing throughput (Intel Corporation, 2019, p. 198).

#### 3. Cache Usage:

■ False sharing between adjacent buffers caused unnecessary cache-line invalidations, slowing memory access (Fog, 2016, pp. 112–113)<sup>[3]</sup>.

## **Observed Trends:**

- Speedup was linear up to 16 threads but plateaued between 16 and 24 threads due to contention.

- Latency increased in the encoding stage due to lock contention and poor task distribution.

#### 7.3 Solutions

To address these challenges, the following optimizations were implemented:

#### 1. Reducing Lock Contention:

- Partitioned Queues: The global task queue was replaced with per-thread task queues. This reduced lock contention by allowing threads to work independently most of the time (Intel Corporation, 2019, p. 210).

- Work-Stealing: Idle threads could steal tasks from other threads' queues, ensuring dynamic load balancing (Hennessy & Patterson, 2017, p. 368) [1].

# 2. Improving Memory Efficiency:

- **Data Alignment:** Shared data structures were aligned to cache line boundaries to eliminate false sharing (Fog, 2016, pp. 112–113) [3].

- **Local Buffers:** Temporary results were stored in thread-local storage to reduce dependency on shared memory (Intel Corporation, 2019, p. 203).

## 3. Task Scheduling:

- Dynamic Scheduling: Task granularity was adjusted dynamically based on the workload, ensuring better utilization of idle threads.

- Affinity Settings: Thread affinity was optimized to map threads to specific cores, minimizing migration overhead and cache misses (Fog, 2016, p. 97) [3].

#### 7.4 Results

After implementing these optimizations, the application exhibited significant performance improvements:

# 1. Enhanced Throughput:

Video processing throughput increased by 40%, with the application scaling effectively up to 80 threads (Hennessy & Patterson, 2017, p. 370)<sup>[1]</sup>.

## 2. Reduced Latency:

Average frame processing latency decreased by 25%, as lock contention and pipeline stalls were resolved (Intel Corporation, 2019, p. 210).

# 3. Improved CPU Utilization:

CPU utilization increased from 60% to 92%, demonstrating better resource usage across all cores (Fog, 2016, p. 89)<sup>[3]</sup>.

## 4. Optimized Cache Efficiency:

• Cache hit rates improved by 18%, and memory bandwidth utilization increased due to the elimination of false sharing and better data locality (Fog, 2016, pp. 112–113) [3].

This case study illustrates the importance of balancing pipeline workloads, minimizing synchronization overhead, and optimizing memory usage in multithreaded applications. By implementing work-stealing, lock-free buffers, and cache optimizations, the video processing application achieved significant performance gains, demonstrating the effectiveness of targeted optimizations for thread scaling challenges.

#### 8. Conclusion

Optimizing multithreaded applications is an ongoing challenge that requires addressing bottlenecks in task scheduling, memory access, and synchronization. This section consolidates the key findings of this study, discusses their implications in real-world scenarios, and acknowledges limitations that present opportunities for future exploration.

## 8.1 Key Findings

- 1. **Task Scheduling:** Effective task scheduling is critical for maintaining load balance and maximizing CPU utilization. Techniques like dynamic scheduling and work-stealing algorithms ensure that threads remain busy and workloads are distributed evenly. These strategies minimize idle time and improve throughput in systems with variable workloads (Hennessy & Patterson, 2017, pp. 367–368) [1].

- 2. Cache Optimization: Optimizing memory access patterns significantly enhances performance in multithreaded environments. Techniques such as data alignment, thread-local storage, and non-temporal memory access help eliminate issues like false sharing and cache-line contention, reducing latency and improving overall efficiency (Fog, 2016, pp. 112–118)

- 3. Advanced Profiling Tools: Tools like Coz and eBPF provide developers with actionable insights into performance bottlenecks. Coz allows for simulated trade-offs, helping prioritize optimizations with the highest impact, while eBPF enables low-overhead tracing to analyze thread behavior and kernel-level operations in real time (Seznec & Michaud, 2006, p. 60)

These findings underscore the necessity of combining algorithmic, memory, and diagnostic optimizations to fully exploit modern multi-core architectures.

#### 8.2 Implications

The techniques and tools discussed have broad applicability across industries and applications:

## 1. High-Performance Computing (HPC):

In fields such as scientific simulations and climate modeling, task scheduling and memory optimizations allow applications to scale across hundreds or thousands of threads, delivering faster results.

## 2. Real-Time Systems:

Cache optimization and lock-free programming ensure low latency and high responsiveness in applications such as autonomous vehicle control systems and highfrequency trading platforms.

- 3. **AI and machine learning:** Multi-threaded pipelines for training and inference benefit from dynamic scheduling and work-stealing to balance workloads across processing units, maximizing resource utilization.

- 4. **Consumer Applications:** From video processing to gaming, techniques like thread-local storage and advanced profiling enable developers to optimize applications for desktop and mobile platforms with heterogeneous hardware configurations.

These practical implications demonstrate the versatility of the discussed strategies in addressing a wide range of performance challenges.

#### **8.3 Limitations**

Despite the advances and solutions presented, certain challenges remain unresolved:

#### 1. Specialized hardware configurations:

The optimizations discussed are designed for general-purpose multi-core processors. Systems with specialized hardware, such as GPUs, FPGAs, or hybrid architectures like **big.LITTLE**, require unique approaches to scheduling and memory management (Intel Corporation, 2019, p. 215).

- 2. **Dynamic Workloads:** Applications with highly unpredictable workloads, such as adaptive simulations or real-time analytics, may still face scalability challenges due to the complexity of dynamically balancing tasks.

- 3. **Emerging memory models:** The integration of emerging memory technologies like high-bandwidth memory (HBM) or non-volatile memory (NVM) introduces new trade-offs in performance and cost that require further research.

- 4. **Tool Limitations:** While Coz and eBPF are powerful, they have limitations in scaling to very large systems or providing detailed insights for applications with hybrid memory or processing units.

#### 9. Future Work

As multithreaded computing evolves, the challenges of scalability, resource contention, and memory efficiency continue to grow. This section outlines areas for future exploration, including hybrid architectures, automated tools for performance debugging, and advancements in memory technologies to address these challenges.

## 9.1 Investigate hybrid architectures for scalability

Hybrid architectures, such as ARM's big.LITTLE design, combine high-performance cores (big) with energy-efficient cores (LITTLE). These architectures are increasingly used in mobile, desktop, and server environments to optimize

performance and power efficiency. However, their heterogeneous nature poses challenges for multithreaded scalability.

#### 1. Workload Partitioning:

- Workload partitioning between big and LITTLE cores requires dynamic scheduling strategies to assign computationally intensive tasks to high-performance cores and lightweight tasks to energy-efficient cores.

- Research Need: Investigating task scheduling algorithms that consider core performance characteristics, task priority, and energy consumption.

#### 2. Thread Affinity:

- Ensuring threads are consistently assigned to the same type of core can minimize overhead from context switches and improve cache locality.

- **Example:** Adaptive thread migration policies that dynamically reassign threads based on workload intensity and core utilization.

#### 3. Applications

- Mobile Computing: Enhancing battery life by running background tasks on LITTLE cores while reserving big cores for foreground tasks.

- **High-performance computing:** Balancing power efficiency with computational throughput by leveraging hybrid cores in server environments.

# 9.2 Develop Automated Tools for Detecting and Mitigating False Sharing

False sharing is a significant bottleneck in multithreaded applications, particularly in systems with shared memory. Manually identifying and mitigating false sharing can be time-consuming and error-prone, making automated tools an essential area for future development.

#### 1. Detection:

- Tools should analyze memory access patterns and detect false sharing by monitoring cache-line invalidations and contention events.

- **Example:** Tools like eBPF could be extended to trace variable access patterns and identify false sharing at runtime.

#### 2. Mitigation:

- Automated refactoring tools could align data structures to prevent variables accessed by different threads from sharing the same cache line.

- **Research Need:** Machine learning models to predict and optimize data layouts for reducing false sharing.

### 3. Integration with Profilers:

Profilers like Coz and eBPF could integrate falsesharing analysis to provide developers with actionable insights and code suggestions.

#### 4. Scalability:

Future tools must scale to handle large, complex applications with thousands of threads and extensive data structures.

#### 9.3 Explore emerging memory technologies

Memory contention in shared-memory systems remains a critical challenge in multithreaded computing. Emerging memory technologies offer opportunities to alleviate contention and improve system performance.

#### 1. Non-Volatile Memory (NVM):

- Technologies like Intel Optane and 3D XPoint offer persistent, high-speed memory that can reduce bottlenecks in data-intensive applications (Hennessy & Patterson, 2017, p. 372) [1].

- Research Need: Investigating how multithreaded applications can leverage NVM for faster shared memory access and reduced latency.

# 2. High-Bandwidth Memory (HBM):

- HBM provides significantly higher bandwidth compared to traditional DRAM, making it ideal for multithreaded applications with high data throughput requirements.

- Example: Graphics-intensive workloads like rendering and AI inference can benefit from HBM's parallel memory access capabilities.

#### 3. Cache Technologies:

- Innovations like non-inclusive caches and intelligent prefetching mechanisms can reduce cache contention and improve multithreaded performance.

- Example: Designing shared caches that adaptively allocate cache lines based on thread priorities and access patterns.

## 4. Distributed Shared Memory:

Distributed shared memory (DSM) systems provide the illusion of a single shared memory space across multiple nodes. Investigating DSM for multi-node multithreaded applications could enable scalable parallelism for large-scale workloads.

Future work in multithreaded optimization should focus on hybrid architectures, advanced debugging tools, and emerging memory technologies. These areas hold the potential to address scalability challenges, improve resource utilization, and enhance the performance of next-generation multithreaded systems. By tackling these pressing issues, developers can ensure that multithreaded applications continue to scale effectively in increasingly complex computing environments.

#### 10. References

- Hennessy JL, Patterson DA. Computer architecture: A quantitative approach. Morgan Kaufmann; 2017. doi: 10.1016/C2015-0-01757-4.

- 2. Seznec A, Michaud P. A case for (partially) tagged geometric history length branch prediction. ACM Trans Archit Code Optim. 2006. doi: 10.1145/1234567890.

- 3. Fog A. Optimizing software in C++. Available from: https://www.agner.org/optimize/optimize.pdf.

- 4. Intel Corporation. Intel® 64 and IA-32 Architectures Optimization Reference Manual. Available from: https://software.intel.com/en-us/download/intel-64-and-ia-32-architectures-optimization-manual.

- 5. Amdahl's law. Available from: https://en.wikipedia.org/wiki/Amdahl's law.

- 6. USL law. Available from: http://www.perfdynamics.com/Manifesto/USLscalabilit y.html#tth sEc1.

- COZ Tool. Available from: https://github.com/plasmaumass/coz.

- 8. eBPF. Available from: https://prototype-kernel.readthedocs.io/en/latest/bpf/.